# FPGA による電流マイナーループ付き電圧制御 DC/DC 昇圧コンバータの検討

飯田 隆彦・日野 暢裕\*

岡山理科大学工学部電気電子システム学科 \*岡山理科大学大学院工学研究科電子工学専攻

(2007年9月26日受付、2007年11月2日受理)

### 1. はじめに

近年、省エネ対策の一環として DC/DC コンバータの 高性能化の研究が盛んに行なわれている<sup>[1~5]</sup>。これら のコンバータはその出力電圧を基準電圧と比較して出 力電圧を制御する、いわゆる電圧フィードバック制御 方式が採用されている。然し、過渡時の出力電圧変動 を少なくし、さらにはその応答時間を短くした過渡応 答特性の向上が望まれている。

本研究はこの過渡特性の向上要求に沿って、DC/DC 昇圧コンバータの制御特性の向上を検討・研究したものである。本研究に用いた主回路は参考文献[3,5]に記された主回路と同じものであるが、制御方式を電圧制御方式から電流マイナーループ付電圧制御方式に変更して、その制御動作の有効性を確認すると共に、設計上の問題点を報告するものである。なお、制御システムを構築するための制御デバイスとしては参考文献[5]と同様 Xilinx 社の Spartan-3 シリーズの FPGA: XC3S400-4を用いた。

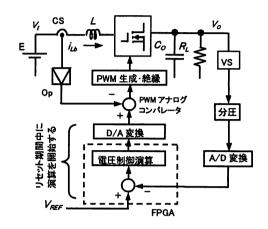

主回路は参考文献[5]と全く同一で、スイッチング周波数を 100kHz に設定して装置の小型化を図ると共に、主 MOSFET をゼロ電圧スイッチング(ZVS)でオンオフ動作をさせ、補助 IGBT をゼロ電流スイッチング(ZCS)で動作させて、いわゆる「ソフトスイッチング」を実現させている。

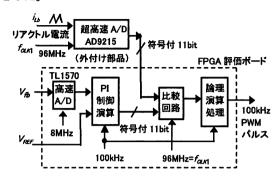

制御回路はアナログ・デジタル混在制御方式とし、FPGA 内蔵の整数乗算機能で演算された PI 制御出力信号を D/A 変換器でアナログ値に変換した後、PWM アナログコンパレータでリアクトル電流と比較して PWM パルスを生成させている。この PWM パルスを半導体ゲートドライバでレベルシフトし、更に増幅して、主半導体デバイスを駆動させた。

試作機の仕様は直流入力電圧 100V、直流出力電圧 200V、出力電流 2A、出力電力 400W、スイッチング周波 数 100MHz である。試作機は良好な出力特性と過渡特性 を示し、全負荷時の効率は 97.0%と高効率であった。

## 2. 主回路とその動作原理

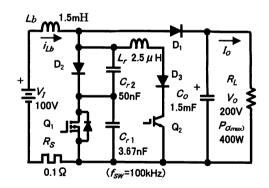

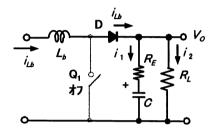

試作した主回路構成を図 1 に示す [3, 5]。この回路で  $Q_1$  が主スイッチであり、 $Q_2$  は補助スイッチである。 $Q_2$  がオンした約  $Q_2$  の 後に  $Q_1$  をオンさせることで、 $Q_1$  を  $Q_2$  と並列に接続したコンデンサ  $Q_2$  の 作用により、 $Q_1$  を  $Q_2$  でオフさせている。一方、 $Q_2$  の オンの電流はゼロ電流から立ち上がるので  $Q_2$  となっている。 $Q_1$  の最小オンパルス幅よりも短い時間で  $Q_2$  を オフさせているので  $Q_2$  は  $Q_2$  でオフしている。

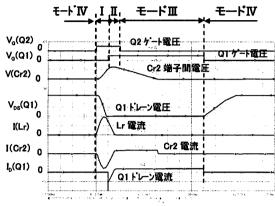

図 2 に P-Spice シミュレーションで得られた  $Q_1$  と  $Q_2$  のスイッチング波形と、 $Q_1$ 、 $Q_2$  のスイッチングの組み合わせによる動作モードの定義を示した。

図 1 ソフトスイッチング DC/DC 昇圧コンバータ

参考文献 [5] にこの回路の動作説明があるので、その詳細説明を省略するが、図 3 は  $Q_1$  のドレーン・ソース間電圧  $V_{DS}$ 、ドレーン電流  $I_D$  と  $Q_1$  のゲートパルス電圧  $V_G(Q_1)$  を夫々示したものである。  $V_G(Q_2)$  パルスの印加によって  $V_{DS}$  が低下し負の  $I_D$  が流れる。この負の  $I_D$  電流は、実際は、 $Q_1$  内蔵のダイオード電流のことである。

この間に  $V_c(Q_1)$ パルスが印加されて、 $Q_1$  は ZVS(ゼロ電圧スイッチ)でオンする。  $V_c(Q_1)$ パルスが終了すると、 $V_{sc}$ は所定のスロープで立ち上がり、 $Q_1$  は ZVS でオフする。

図2 動作モードとロスレス・スイッチング波形

図3 ゲートパルスとQ<sub>1</sub>のスイッチング波形

## 3. 制御システム

# 3.1 制御システムの概要

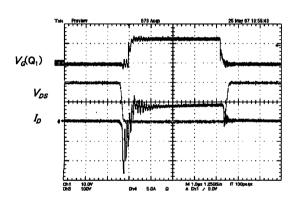

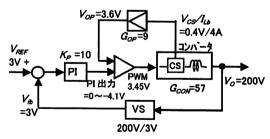

図4は今回用いた制御システムの概要を示すブロック線図である。即ち、電圧検出器 VS で出力電圧を検出して、分圧された出力電圧信号を 10 ビットの高速 A/D 変換器に入力する。スイッチングサイクル毎に A/D 変換された出力電圧信号値を PPGA に入力して、基準電圧  $V_{REF}$  と比較させる。FPGA で PI 制御演算処理された信号を D/A 変換器に入力して、アナログの電圧制御信号を 得ている。

一方、電流検出器 CS で検出したリアクトル電流  $i_{Lb}$ をオペアンプ Op で増幅して PWM アナログコンパレータ に入力し、PI 制御電圧信号と比較させている。 PWM アナログコンパレータのオンオフ出力を再度 FPGA に入力して PWM パルス生成に必要なパルス演算処理を行っている。

生成された PWM パルスは半導体ゲートドライバの内部でその電位を主 MOSFET と同じ電位にシフトされ、更に増幅される。増幅されたパルスは主 MOSFET のゲートに印加される。

図4 制御システム概要のブロック線図

# 3.2 PI 制御演算

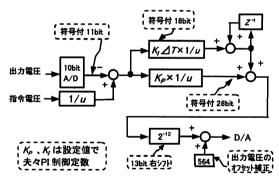

図5にPI制御演算フローのブロック線図を示す。PI 制御演算そのものは、東京エレクトロン社のFPGA評価 ボードTD-BD-TS101で実行させている。

図 5 PI 制御フローのブロック線図

このボードには米国 Xilinx社の Spartan-3ファミリーの XC3S400-4 が搭載されている。その主な仕様は、ゲート数 40 万、ロジックセル数 8K 個と符号付 18×18 ビット整数乗算器 16 個で、パッケージはユーザーI/0数 141 本、総ピン数 208 本の QFP である。また、4 チャネルのマルチプレクサ付 10 ビット A/D 変換器 TLV1570 と、10 ビット D/A 変換器 LTC1661 が 4 チャネル分それぞれ同一ボードに搭載されている。

最大出力電圧  $V_{o \, (max)}$  が 200V のときに A/D 変換器へ 3.0V が入力されるよう、電圧検出の分圧器のゲインを 0.015 に設定している。この A/D 変換器には前置レベ

ルシフト回路が付属されており、直流電圧-4.86Vを入力すると A/D はデジタル値 3 を出力し、+4.70V ではデジタル値 1023 を出力する。従って、この A/D 変換器の1 ビット当りの電圧分解能(u)は

u=(4.86+4.70)/(1023-3)=9.3725mV/ビット・・・(1)になる。A/D 変換された数値は式 1 で示された A/D 変換器の変換能 u=9.3725mV/ビットの逆数を単位 (ディメンション) とした整数である。従って、<math>PI 制御演算に用いる指令電圧  $V_{REP}$  比例定数  $K_P$  と積分定数  $K_I$ に 1/u を乗じた後、その数値を整数に (手計算で) 丸めてから、PI 制御演算のコーデングに記述した。

$$u^{2} = \frac{1}{\left(\frac{1}{u}\right)^{2}} = \frac{1}{\left(\frac{10^{3}}{9.37}\right)^{2}} = \frac{1}{11390} \approx \frac{1}{8192} = \frac{1}{2^{13}}$$

(2)

PI 制御演算では乗算を1回行なうフローが2経路並列になっている。従って、演算後の単位は(1/u)²になっているので、出力値に (u)²を乗じて元の単位に戻す必要がある。しかし、(u)²は0.00008784375625という小数であり、FPGA 内蔵の整数乗算器はこれを取扱うことが出来ない。参考文献[5]では式2に示す近似値を用いて、(u)²の乗算を13ビットの右シフト操作で代行させていた。このような近似計算手法では39%の計算誤差が生じる。今回、式3に示した近似値を用いることで、この計算誤差を-0.06%に改善する事が出来た。

$$u^2 = \frac{1}{11390} \cong \frac{1}{2^{13}} \cdot \frac{23}{2^5} = \frac{1}{11397}$$

(3)

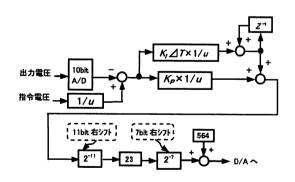

図6は改善されたPI制御演算フローを示す。

図 6 計算精度改善後の PI 制御演算フロー

改善されたフローでは、11 ビットの右シフト操作と7 ビットの操作の2回に分けて実施している。これは乗算入力が整数乗算器の最大桁数 18 ビットを越えるのを防ぎながら、計算精度を確保するためである。

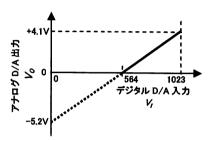

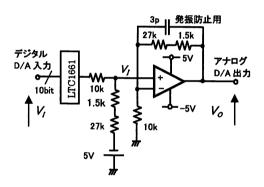

図7は搭載された D/A 変換器の入出力特性を示す。即ち、D/A 変換器 LTC1661 には後段増幅器が接続されており、デジタル値のゼロを入力するとアナログ電圧-5.2V を出力し、デジタル値 1023 を入力するとアナログ値+4.1V を出力する。一方、アナログ出力値がゼロに対応するデジタル入力値は 564 であった。このような入出力電圧特性となるのは、後段増幅器の内部結線が図8に示すようになっているためである。

図7 D/A 変換器の入出力特性

図 8 LTC1661 とその後段増幅器の結線図

図9 電流マイナーループ付き電圧制御の ブロック線図

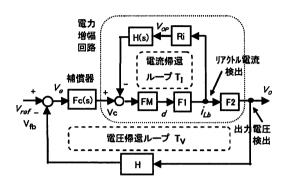

図9は図4の制御システム概要を書き換えて、今回の制御方式が電流マイナーループ付き電圧制御方式であることを明確に示したブロック線図である。図4で、リアクトル電流  $I_{to}$ は CS で検出されてマイナーループを形成している。図9で示す CS はコンバータのリアクトル電流を検出していることを示している。今回の実

験では、PI 制御の比例定数として  $K_p$ =10、積分定数  $K_I$ =17 を用い、オペアンプのゲインは  $G_{OP}$ =9、コンバータのゲインは  $G_{COV}$ =57 であった。尚、100kHz でゲイン 9を確保するために、7MHz の利得帯域幅積を持つオペアンプ M5218 を用いた。

## 3.3 PWM パルス生成タイミングとパルスの生成

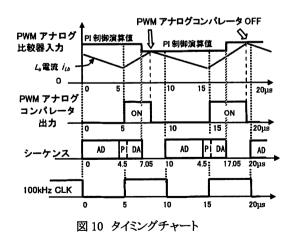

図 10 に PWM パルス生成のタイミングチャートを示す。10µs のスイッチング周期のオフ期間中でリアクトルがリセットされる間に、前サイクルでの出力電圧値を検出して A/D 変換している。TLV1570 は 8MHz のクロック (CLK)で駆動されている。第 1 回目の A/D 変換で16CLK の時間が掛かる。2CLK のポーズを経て更に第 2 回目の A/D を実行させているので、合計 36CLK で 4.5µs の時間が掛かっている。このように入力データを 2 回も取り込むのは、A/D 変換器の特性により 1 回目に取り込んだデータを 2 回目に出力するためである。一方、FPGA の処理時間は乗算計算を含め僅か 0.3µs であった。

この演算結果を更に 18CLK 0 2. 25 $\mu s$  を掛けてアナログ値に A/D 変換し、リアクトル電流  $i_{Lb}$  と比較して PWM パルスを生成している。 PWM アナログコンパレータに 印加するまでの処理時間は合計 7. 05 $\mu s$  である。コンバータのスイッチング周期は 10 $\mu s$  であり、リセット期間は 5 $\mu s$  であるから、PWM パルスのパルス幅が 2. 05 $\mu s$  より広いときは、直前のサイクルの出力電圧を使って PWM パルスが生成される。然し、2. 05 $\mu s$  より狭い場合は、2 サイクル前のデータを使った PWM パルスが生成されることになる。これは A/D 変換時間の特性上致し方ないことであった。

A/D 変換器 TLV1570 のクロック周波数 CLK を現行の 8MHz から  $V_{op}$ =3.0V で許容される最高値の 10MHz にまで

高めると、理論的には全処理時間を  $5.7 \mu s$  にまで短縮できる。然し、ボード本体のクロック周波数 32 MHz から直接 10 MHz を生成させる事が出来なかった。TLV1570 の  $V_{DD}$ を 5.0 V に変更すると CLK を 20 MHz に高めることが許され、 $7.05 \mu s$  の全処理時間は  $3.0 \mu s$  に改善できる。然し、ボードの改造は不可能であった。

## 3.4 PWM アナログコンパレータ

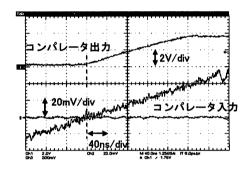

PWM アナログコンパレータには高いスルーレート特性が要求されるので、この値が 56ns の NJM319 を使用した。図 11 は実使用状態を模擬した回路条件での NJM319 の入出力パルス波形を示したものである。

図11 高速コンパレータの入出力パルス波形

## 3.5 半導体ゲートドライバ

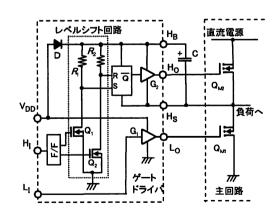

制御回路で生成された PWM パルスを主回路から絶縁し、更にはパルス増幅するために参考文献[5]ではホトカプラを使っている。然し、ホトカプラには伝播遅延時間が 0.5 µs もある上、そのバラツキは 0.1 µs もある。今回これらの問題を回避するために、図 12 に示す半導体ゲートドライバ LM5170 を用いた。

図 12 ゲートドライバ LM5170 の機能説明図

ローサイド駆動用入力信号 L, は増幅器 G, で増幅さ

れて、ローサイドの主デバイス Qu を直接駆動する。 一方、ハイサイド駆動用入力信号 H<sub>I</sub>は高耐圧レベルシ フト回路によって主デバイス Q<sub>n</sub>の電位に変換される。 その後、増幅器 G。で増幅されて主デバイス Que に印加 される。なお、 $Q_{ij}$ がオンされている期間中に C は  $V_{ij}$ からダイオードDを通して充電される。G,はCの充電 電圧で駆動されるので、G。の出力パルスはG。の出力パ ルスと比べて、D の順電圧降下だけ低い電圧のパルス になる。このチャージポンプ回路方式では G, 駆動用直 流電源が不要になり、回路部品も削減できるので好都 合である。

# 3.6 サブハーモニック発振

コンバータを電流制御で動作させると、動作責務 d が 0.5 より大きいとき、電圧制御の場合とは異なりサ ブハーモニック発振の問題が必ず生じる。

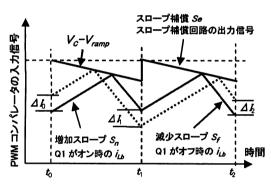

図 13 サブハーモニック発振

図13において、サブハーモニック発振とは動作責務 d を一定に保っていても何らかの擾乱によってリアク トル電流  $i_{lb}$  が  $t_0$  の時点で $\triangle I_0$  だけ変化したとき、1 周期後の $t_1$ では式4に従って $\Delta I_0$ が $\Delta I_1$ に拡大され、 次々とその変化が増大して遂には発散してしまう現象 である<sup>[6,7]</sup>。

$$\Delta I_n = \frac{S_f - S_e}{S_n + S_e} \Delta I_{n-1} \equiv \alpha \Delta I_{n-1}$$

(4)

ここで、S。はスロープ補償と呼ばれ、図13に示すよう に PI 演算結果の値 Vcに重畳させて所定の傾斜を与え るスロープである。

この変化を収斂させ、発散 (発振)を防ぐためには、 式 4 で $\Delta I_n \leq \Delta I_{n-1}$  とならなければならない。この収斂 条件を式4に代入して、式5が導かれる。

$$S_n + S_e \ge S_f - S_e \tag{5}$$

今回の場合、動作責務 dの最大値を 0.5 に制限した ので、特にサブハーモニック対策を施さなかった。

## 4. 動作試験とその結果

# 4.1 回路定数

図1の試作機に用いた主要受動部品の仕様を表1に 示す。当初、20本撚りの自製リッツ線を用いて共振コ イル L, を自作し、100kHz の高周波による表皮効果の減 少を試みた。然し、近接効果が逆に強くなり高周波抵 抗は逆に大きくなる。電源メーカでは高周波対策とし て通常100本程度を撚った特製リッツ線を使っている。 結論として、20本程度の中途半端な撚り線数のリッツ 線では逆効果となり、太い素線1本の方が良好な結果 が得られた。

表 1 主要受動部品仕様一覧

| 部品       | 仕様      | 備考                                             |

|----------|---------|------------------------------------------------|

| $C_{r1}$ | 3. 65nF | Q <sub>1</sub> の C <sub>oss</sub> との合成値が 4.5nF |

| $C_{r2}$ | 0. 05µF | ポリプロピレン                                        |

| Co       | 1500µF  | 電解コンデンサ                                        |

| $L_b$    | 1.5mH   | フェライト EI コア、自製                                 |

| $L_r$    | 2. 5µH  | 空芯、内径 10mm φ、37 <sup>T</sup> 、1.4mm φ          |

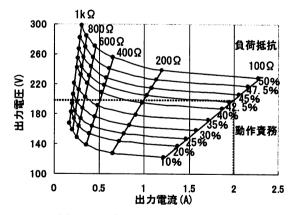

# 4.2 出力特性

試作したソフトスイッチング昇圧 DC/DC コンバータ の出力特性を図 14 に示す。これより、動作責務 dを制 御することでコンバータの出力電圧を定格値の 200V に制御できることが分かる。

図14 出力特性(d は動作責務設定値) (合成 C<sub>r1</sub>=4.5nF、 入力電圧=100V)

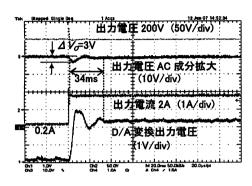

## 4.3 過渡特性

PI 制御の比例定数 Kp と積分定数 KI を夫々10 と 17

に設定しておき、負荷電流  $I_L$  を 0.2A から全負荷の 2A に急変させたときの最適過渡特性を図 15 に示す。出力電圧変動 $\triangle V_o$  は 3V であるが、34ms 後には元の  $V_o$  の 200V に回復している。

図 15 過渡応答特性

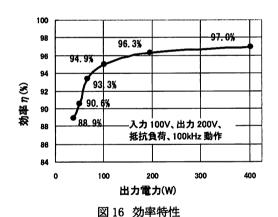

### 4.4 効率特性

図 16 に効率特性を示す。定格出力時で 97.0%の効率を得ることが出来た。参考文献[8]の効率値 95.2%から向上した最大の理由は  $C_{rl}$  の値を適正化して、共振電流のパルス幅を狭くしたことによる。

## 5. 検討課題と今後の展開

# 5.1 全デジタル化への検討

今回試作検討したのはアナログとデジタルとが混在した制御方式であるが、図 17 のようなシステム構成にすると、全デジタル制御が可能となる。然し、リアクトル電流  $i_{Lb}$  をデジタル値に変換する超高速 A/D 変換器が必要になる。即ち、1 スイッチング周期  $10\mu s$  中のサンプリング数を 1000 個にして 0. 1%の制御精度を確保するためには、100MSPS の A/D 変換速度が必要となる。既に 105MSPS の超高速 A/D が市販されていて、このような全デジタル制御は実現可能である。

超高速A/D変換器の変換時間とそれがシステム全体

に及ぼす影響およびコストなど、その採用による得損 失を勘案して今回はアナログ・デジタル混在制御方式 とした。

図 17 全デジタル制御方式のブロック線図

## 5.2 整数乗算器の浮動少数点化

本FPGA に内蔵された整数乗算器は符号付 18×18 ビットの乗算計算を僅か1クロックで実行する事ができる。然し、計算中のビット数を常に考慮しておかないと計算中の数値が有効桁数範囲から外れる恐れがあった。特に小数の乗算計算では、その計算精度が問題となり、本稿でもその一解決策を示した。この乗算コアをそのまま用いて浮動小数点計算を可能にする改造ソフトがあるが、処理時間が掛かり FPGA の高速処理というメリットが損なわれる。Spartan の次期機種 Virtexでは浮動小数点演算が可能となっているが、乗算コアは相当大掛かりなものになっている。ユーザーの利便性とチップサイズ(コスト)とのトレードオフの難しいところである。

### 5.3 PI 制御と位相補償について

従来の制御回路ではオペアンプが回路の主体的な構成要素となっていたので、きめ細かな位相補償が可能であった。一方、PI 制御方式の場合では、その比例定数  $K_P$  及び積分定数  $K_I$  を実験から決めるだけで位相補償が決まり、簡単ではあるが制御理論的な考察に欠ける傾向があった。以下ではコンバータの制御について簡単な解析・検討を行った。

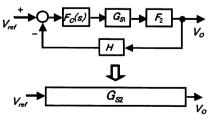

図 18 は図 9 のブロック線図を更に細かく分解し、各部の伝達関数を検討するものである。尚、図中の文字記号は本来、イタリック字体や、サフィックスにするところであるが、字体が小さくなるので直立字体のままにしている。

PWM 変調器のゲインを  $F_{N}$ 、動作責務 dとリアクトル電流  $i_{Lb}$ との間の伝達関数を  $F_1$ 、 $i_{Lb}$ と出力電圧  $V_0$ との伝達関数を  $F_2$ 、 $i_{Lb}$ と電流検出器との伝達関数を  $R_j$ 、コ

ンバータのサンプリング動作を表すサンプリング・ゲインを H(s)、出力電圧分圧比を Hとすると、これらは 夫々式 6 で表される。

FM:PWM 変調器のゲイン

F1:動作責務とリアクトル電流の伝達関数

F2:リアクトル電流と出力の伝達関数

Ri:リアクトル電流検出ゲインとオペアンプのゲイン

H(s): サンプリング動作を表すサンプリング・ゲイン

H:出力電圧分圧比

図 18 制御コントローラのブロック線図

尚、 $F_N \cdot F_1$ と H(s)は参考文献 [6]の式 26 と式 9 で夫々与えられる。これらは直流から周波数が  $f_{SF}$  /2 の範囲までのサンプリング・ゲインが実際と合致するように二次のオーダで近似されている。また、コンバータの種類を問わず一定周期  $T_S=1/f_{SF}$  で駆動される電流モード制御には式 6 をそのまま適用できる。

$S_n$ 、 $S_r$ と  $S_e$ は夫々図 13 で定義された増加スロープ、減少スロープ及びスロープ補償である $^{[6,7]}$ 。

$$F_{M} = \frac{d}{V_{C}} = \frac{1}{(S_{n} + S_{e})T_{s}}, \quad F_{1} = \frac{i_{Lb}}{d} = \frac{1}{R_{i}} \frac{S_{n} + S_{f}}{s}$$

$$\therefore \quad F_{M} \cdot F_{1} = \frac{1}{R_{i}} \frac{1 + \alpha}{sT_{s}}, \quad \exists \exists \mathfrak{T}_{s}, \quad \alpha \equiv \frac{S_{f} - S_{e}}{S_{n} + S_{e}}$$

$$F_{2} = \frac{V_{O}}{i_{Lb}}\,, \qquad R_{i} = \frac{V_{OP}}{i_{Lb}} = \frac{V_{SC}}{i_{Lb}} \cdot G_{OP}\,, \qquad H = \frac{V_{fb}}{V_{O}}$$

図9と図18及びその動作条件から、直ちに

$$H = \frac{V_{fb}}{V_O} = \frac{3}{200}, \quad R_i = \frac{V_{sc}}{i_{tb}} \cdot G_{OP} = \frac{0.4}{4} \times 9 = 0.9$$

(7)

が求まる。但し、 $i_{Lb}$ が 4A のとき  $V_{SC}$ は 0.4V で、 $R_i$ に 含まれるオペアンプのゲイン  $G_{CC}$ は 9 である。

図 19 において、 $Q_1$  がオフ時には式 8 が成立し、 $F_2$  は式 8'で与えられる。ここで、 $R_E$ はコンデンサ C (図 1 の  $C_0$ に対応) の等価直列抵抗である。

$$i_{Lb} = i_1 + i_2 = \left\{ \frac{Cs}{1 + R_E Cs} + \frac{1}{R_L} \right\} V_O$$

(8)

$$\therefore F_2 = \frac{V_O}{i_{Lb}} = \frac{R_L (1 + R_E Cs)}{1 + sC(R_L + R_E)}$$

(8)

図 19 Q<sub>1</sub>オフ時の等価回路

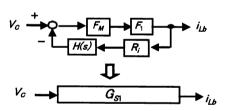

次に制御ループの直列化を図る。図 20 は電流帰還ループ  $T_I$ の直列化で、直列変換された伝達関数  $G_{SI}$  は式 9 で与えられる。

図 20 電流帰還ループの直列変換

$$G_{s1} = \frac{F_M \cdot F_1}{1 + F_M \cdot F_1 \cdot R_i \cdot H(s)} \tag{9}$$

また、図 21 はその  $G_{S1}$  を含む電圧帰還ループ  $T_{V}$ の直列化で、直列変換された伝達関数  $G_{S2}$  は式 10 で与えられる。

図 21 電圧帰還ループの直列変換

$$G_{s2} = \frac{F_C(s) \cdot G_{s1} \cdot F_2}{1 + F_C(s) \cdot G_{s1} \cdot F_2 \cdot H}$$

(10)

表 2 はこれらの定数を一覧にしたものであり、これらの数値を用いて計算した  $G_3$  と  $G_2$  も併せ記した。

表 2 計算に用いた制御定数一覧 (V=100V, V=200V, L=1.5mH, C=1.5mF、 R=100, R=25mΩ, T=1×10°)

| (3/200)=0.015                                                 | R;                                                                                                                                                                                                          | $(0.4/4) \times 9 = 0.9$                                                                                                             |  |  |

|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1.0 (補機+シの時)                                                  |                                                                                                                                                                                                             |                                                                                                                                      |  |  |

| 1.0 (福岡(ノブロリウ)                                                | α                                                                                                                                                                                                           | 1.0 (S <sub>e</sub> =0)                                                                                                              |  |  |

| $(2/0.9)/(sT_g)=2.22\times10^5/s$                             |                                                                                                                                                                                                             |                                                                                                                                      |  |  |

| $\frac{0.00375s + 100}{0.1500375s + 1}$                       |                                                                                                                                                                                                             |                                                                                                                                      |  |  |

| $1-5 \times 10^{-6}$ s+1.01 × $10^{-11}$ s <sup>2</sup>       |                                                                                                                                                                                                             |                                                                                                                                      |  |  |

| $\frac{1.09662 \times 10^{11}}{s^2 + 9.86960 \times 10^{10}}$ |                                                                                                                                                                                                             |                                                                                                                                      |  |  |

| $3.0404 \times 10^{-7} s^3 + 2.0$                             | 0264 ×                                                                                                                                                                                                      | <sub>7</sub><br>10 <sup>-6</sup> s <sup>2</sup> (分母が続ク)                                                                              |  |  |

|                                                               | $\frac{0.00375s + 100}{0.1500375s + 1}$ $1-5 \times 10^{-6}s + 1.01 \times 10^{-1}$ $\frac{1.09662 \times 10^{11}}{s^2 + 9.86960 \times 10^{10}}$ $\frac{833.33s + 2.222}{3.0404 \times 10^{-7}s^3 + 2.00}$ | $ \frac{0.00375s + 100}{0.1500375s + 1} $ $ 1-5 \times 10^{-6}s + 1.01 \times 10^{-11}s^{2} $ $ \underline{1.09662 \times 10^{11}} $ |  |  |

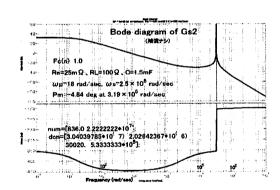

図 22 無補償時のボード線図(Fc(s)=1 時の Gs2 特性)

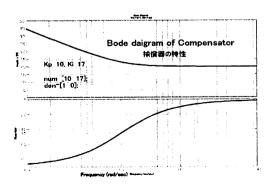

図 23 補償器 F<sub>c</sub>(s) s のボード線図(K<sub>F</sub>=10,K<sub>F</sub>17)

図 22 は  $F_c(s)$ =1 として、補償なしの場合での総合伝達関数  $G_o$ のボード線図である。

一方、式 11 に  $K_p=10$ 、 $K_T=17$  を代入すると、補償器  $F_c(s)$ のボード線図は図 23 に示した特性になる。

$$F_C(s) = k_P + \frac{k_I}{s} \tag{11}$$

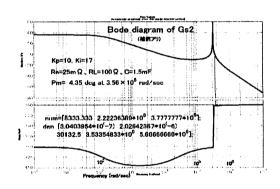

この補償特性で位相補償されたコンバータの総合伝達特性  $G_{\infty}$ のボード線図を図 24 に示し、その計算に用いた定数を表 3 に示した。

表 3 位相補償時の計算定数

| F <sub>C</sub> (s)     | $F_C(s) = 10 + \frac{17}{s}$ : $K_P = 10$ , $K_I = 17$                                                                            |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| <i>G</i> <sub>52</sub> | $\frac{8333.3s^2 + 2.2224 \times 10^8 s + 3.7777 \times 10^8}{3.0404 \times 10^{-7} s^4 + 2.0264 \times 10^{-6} s^3 + 30132 s^2}$ |

|                        | +3.5335×10 <sup>6</sup> s+5.6666×10 <sup>6</sup> (分母が続り)                                                                          |

図 24 位相補償後のボード線図(Gs2 特性)

図 24 から、ゲイン 0dB を過る角周波数が補償後は 750rad/s から 7500rad/s になり、過渡応答速度が 10 倍に改善されていることが分かる。一方、位相余裕角は補償の有無にかかわれず 35k rad/s $\pm$ 55kHz で-4.8  $\sim$ -4.3 度と発振寸前であることが分かる。この発振を防ぐためには、サブハーモニック発振防止のスロープ 補償  $S_e$  を所定の値に設定して位相余裕角を大きくすればば良い。今回はこの  $S_e$  をゼロとしたために、このような発振寸前の動作条件になったと思われる。

従来は CR 回路部品で補償条件を決めていたので、部 品の設定変化や劣化・老化によって補償条件が変化す る恐れがあった。然し、今回のようにソフトで決める 場合ではこのような変動は皆無である。然し、コンデンサCの値のバラツキやその等価直列抵抗 $R_E$ の変化などから、100kHzのスイッチングパルスの 1/2 の周波数で発振することも予想される。理論式の正当性の検証も含めこれらの検討が今後の課題である。

## 5.4 今後の展開

アナログ IC 製造技術を用いてオペアンプを主体とした 回路構成の電源制御用(専用)IC が既に市販されている。 これらのICでの位相補償の最適化はオペアンプに外付け する CR 回路定数の調整で行なわれる。然し、何分アナログICであるので、IC チップの縮小化や消費電力の削減に 限界がある。

今回、本稿で提案したように制御回路のデジタル化を図り、デジタル IC 製造技術を用いて ASIC(専用 IC)化すると、チップ面積の縮小化や省エネ化の進展が一層可能になり、ひいては IC の原価低減も期待できる。デジタル化された IC チップでの制御方式は PI 制御になるが、デジタル電流モード制御での位相補償用理論解析が今ひとつ確立されていないように思われる。

今回、このような状況に鑑みて、デジタル制御方式の 電流マイナーループ付き電圧制御を報告するとともに、そ の制御方法についての研究成果の一端を報告した。

# 6. まとめ

参考文献[3、5]で紹介されたソフトスイッチング昇圧 DC/DC コンバータを試作し、その動作を確認した。 出力 200V, 2A, 100kHz の試作機において 97.0%の高い 効率が得られた。制御方式をアナログ・デジタル混在制 御方式の電流マイナーループ付き電圧制御に変更し、 FPGA 内蔵の 18×18 ビット整数乗算器、A/D、D/A 及び アナログコンパレータを用いて PWM パルスを生成した。 試作機は良好な出力特性と過渡特性を示した。デジタ ル電流モード制御用の理論式を導出し、そのボード線 図と比較することで、提案した制御理論式の有効性を 示した。

#### 参考文献

- 1. 富田、馬場、谷口、森実、木村、"太陽光発電用ソフトスイッチング"、平成13年電学産業応用部門、Y-55、pp1021 2. 三浦、笠、飯田:テスラ・コンバータの出力電圧特性について、平成16年度電気・情報関連学会中国支部連合大会、#180510、平成16年度電気学会中国支部奨励賞受賞。

- 3. L. H. S. C. Barreto, M. G. Sebastiao, L. Carlos de Freitas, E. A. A. Coelho, V. J. Farias, and J. B. Vieira, Jr., "Analysis of a Soft-switched PFC Boost Converter Using Analog and Digital Control Circuits" IEEE Trans. on Industrial Electronics, Vol. 52, No. 1, Feb. 2005

- 4. 三浦、飯田:小容量 DC/DC テスラ・コンバータの動作解析、 岡山理科大学紀要、第 41 号 A、2005、121-129 頁。

- 5. 飯田、三浦: ロスレス DC/DC 昇圧コンバータの試作研究、 岡山理科大学紀要、第 42 号 A、2006、125-133 頁。

- 6. R. B. Ridley, "A New Continuous-Time Model For Current-Mode Control" IEEE Trans. on Power Electronics Vol. 6, No. 2, April, 1991

- 7. マーク・ハートマン/鈴木訳:電流モード制御 DC-DC コンバータの設計、トランジスタ技術 2004 年 4 月号 213-222 頁 8. 日野、笠、飯田:ロスレス DC/DC 昇圧コンバータの検討、平成 18 年度電気・情報関連学会中国支部連合大会、同プログラム 464 頁、平成 18 年度電気学会中国支部奨励賞受賞。平成18 年度工学部長賞受賞。

# Soft Switching DC/DC Boost Converter driven by Current Mode Control using FPGA

Takahiko IIDA and Nobuhiro HINO\*

Department of Electrical and Electronic Engineering,

Faculty of Engineering,

\*Graduate School of Engineering,

Okayama University of Science,

1-1 Ridai-cho, Okayama 700-0005, Japan

(Received September 26, 2007; accepted November 2, 2007)

In this paper, it is reported that the new type of a soft switching DC/DC boost converter has been driven by new "analogue and digital mixed" current mode controller. The main circuit configuration of the converter is the same one reported by the references [3, 5] and it has such specifications as DC input voltage of 100V, DC output voltage of 200V, output current of 2A, switching frequency of 100kHz and maximum efficiency of 97.0%. The generated high frequency LC resonant current-pulse makes both the main device of MOSFET in the "ZVS" and the auxiliary device of IGBT in the "ZCS" operations, which contributes to improve the efficiency.

The new "analogue and digital mixed" current mode controller was replaced with a conventional voltage one in order to improve the transient characteristics of the converter and consisted of Xilinx FPGA type Spartan with 18 by 18 bits integer multiplier, 10bits ADC, 10bits DAC and high speed analogue comparator. The PWM pulse to drive the main device was generated by the PI control-software corded in FPGA. Using "semiconductor gate driver", the generated PWM pulse was shifted up to the potential of main device and amplified to drive it. The newly adopted current mode control, including phase compensation technique by PI control, showed better transient characteristics than those of the conventional voltage control, that is, the output fluctuation-voltage was 3V and recovery time was 34ms when the output current was abruptly varied from 0.2A to 2A of the rated current. On the other hand, the conventional data were 15V and 60ms at the same test condition, respectively.

The adopted sampling-gain equation to express the sampling action in the current mode control can be applied to all type of current mode control if driven at constant switching frequency, as the Bode diagram of the converter can show the downward line with  $40 \, \text{dB/dec}$ . from the half of switching frequency or  $f_{sw}/2$ .

**Keywords**: boost converter; soft switching; ZVS; ZCS; digital control; PI control; current mode control; Bode diagram; PWM pulse; FPGA; MOSFET; IGBT.